Agenda

| 13:30 Uhr | Get Together beim Imbiss |

| 13:55 Uhr | Begrüßung Prof. Dr. Martin Leucker, Universität zu Lübeck |

| 14:00 Uhr | Formal Verification of Embedded Code – Applications and Challenges Thorsten Ehlers, Institut für Informatik, Christian-Albrechts-Universität zu Kiel |

| 14:30 Uhr | Static Analysis of Concurrent Automotive Software Johannes Traub, Daimler AG |

| 15:00 Uhr | Pause |

| 15:15 Uhr | Vorkehrungen für die effiziente Suche nach Software-Defekten sowie für Performance-Optimierungen in Multicore-Systemen Alexander Weiss, Accemic GmbH & Co. KG |

| 16:00 Uhr | Effiziente Überwachung von Laufzeiteigenschaften in Soft- und Hardware Philip Gottschling, TU Darmstadt und Normann Decker, Universität zu Lübeck |

| 16:30 Uhr | WCET on Multicore Processors – Problems and Answers Simon Wegener, AbsInt Angewandte Informatik GmbH |

| 17:00 Uhr | Diskussion beim Imbiss |

| 18:00 Uhr | Ende des Workshops |

Vorträge und Referenten

Thorsten Ehlers, Institut für Informatik, Christian-Albrechts-Universität zu Kiel

Formal Verification of Embedded Code – Applications and Challenge

This talk will introduce some typical concurrency bugs occurring in embedded code. Based on this, it will discuss how formal methods can be applied to find these defects. Here, the talk will especially consider the case of migrating legacy code from single- to multi-core CPUs. Furthermore, they present some code pattern which are typical for embedded code, and discuss their impact on the performance of analysis tools.

Johannes Traub, Daimler AG

Static Analysis of Concurrent Automotive Software

Der Einzug von Multicore-Hardware in Automotive Steuergeräte ermöglicht eine wirkliche parallele Ausführung der Echtzeit-Software. Allerdings birgt diese parallele Ausführung ein stark erhöhtes Risiko für das Auftreten von kritischen Race Conditions. Das Verifikations-Werkzeug MEMICS bietet die Möglichkeit, solche Race Conditions in Automotive Software zu identfizieren. Zusätzlich zur Position des Fehlers wird ein Trace geliefert, welcher die Nachvollziehbarkeit enorm vereinfacht.

Alexander Weiss, Accemic GmbH [&] Co. KG

Vorkehrungen für die effiziente Suche nach Software-Defekten sowie für Performance-Optimierungen in Multicore-Systemen

Selbst bei äußerst sorgfältig programmierten und getesteten Applikation muss davon ausgegangen werden, dass sich auch in fortgeschrittenen Entwicklungsstadien sowie nach dem Release noch immer Defekte im Programmcode befinden. Deshalb sollten in gut geplanten Projekten Vorkehrungen getroffen werden, um Defekte effizient suchen und beseitigen zu können.

Der Vortrag beschäftigt sich mit der Klassifizierung von Defekten, ihrer Auftretenswahrscheinlichkeit vor und nach einem Release sowie ökonomischen Aspekten der Fehlersuche. Weiterhin werden verschiedene Anforderungen an Performance-Optimierungen diskutiert. Voraussetzung dafür ist jeweils eine umfassende Beobachtbarkeit – dies stellt besonders bei Multicore-Systemen eine große Herausforderung dar, da hier die erfassten Abläufe in einzelnen Cores synchronisiert werden müssen, um beispielsweise Wettlaufsituationen untersuchen zu können. Herkömmliche Verfahren wie die Instrumentierung der Software stoßen hier schnell an ihre Grenzen.

Im Vortrag werden Maßnahmen erläutert, die schon beim Entwurf von Hard- und Software getroffen werden sollten, um Multicore-Systeme effizient, flexibel und nicht intrusiv beobachten zu können

Simon Wegener, AbsInt Angewandte Informatik GmbH

WCET on Multicore Processors – Problems and Answers

Bei der Abschätzung der Laufzeit eines Tasks im schlimmsten Fall stellen Mehrkern-Prozessoren eine neue Herausforderung dar.

Dieser Vortrag möchte einige der Probleme aufzeigen, die heutige Multicore-Architekturen mit sich bringen.

Darüber hinaus werden Lösungsansätze vorgestellt, die es ermöglichen sollen, eine Laufzeitabschätzung für zukünftige eingebettete Systeme durchzuführen

Philip Gottschling, TU Darmstadt und Normann Decker, Universität zu Lübeck

Effiziente Überwachung von Laufzeiteigenschaften in Soft- und Hardware

Wir beschreiben das grundsätzliche Vorgehen und Methoden, um Ablaufeigenschaften von Systemen deskriptiv zu spezifizieren und daraus operationale Modelle in Form von sog. Monitoren zu generieren. Ein Monitor verarbeitet Systembeobachtungen und gibt kontinuierlich eine Bewertung hinsichtlich der spezifizierten Korrektheitseigenschaft aus.Um diese in Echtzeit zu überwachen und auszuwerten eignen sich moderne FPGAs, da sie sich beliebig oft neu konfigurieren lassen. Die nicht triviale Hardwarebeschreibung und die damit verbundenen Entwicklungswerkzeuge stellen allerdings für die meisten Nutzer ein großes Hindernis dar. Durch Abstraktion und Integration lässt sich dieses überwinden und stellt diese Technologie einem breiteren Anwenderfeld zur Verfügung.

Veranstaltungsort

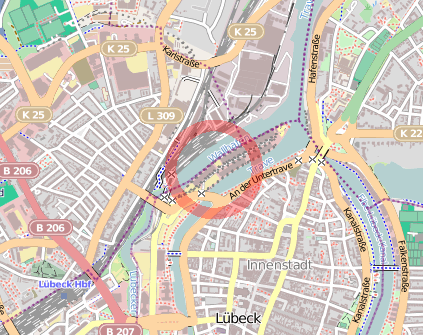

media docks

Willy-Brandt-Allee 31a

23554 Lübeck

Anfahrtsskizze

© OpenStreetMap-Mitwirkende (Lizenz: CC-BY-SA)

Bing Karten

Lageplan Media Docks Lübeck

Anmeldung

Die Teilnahme an der Veranstaltung ist kostenfrei. Da eine begrenzte Anzahl der Plätze zur Verfügung steht und zur besseren Organisation des KoSSE-Workshops bitten wir um verbindliche Anmeldung bis zum 09. Dezember 2014 unter: